#### BBDEV. MEMO #023

# Massachusetts Institute of Technology Haystack Observatory WESTFORD, MASSACHUSETTS 01886

25 February 2009 Updated: 15 October 2015

To: Broadband Development Group

From: A.E.E. Rogers

Subject: Tests of new "digital" phase calibrator.

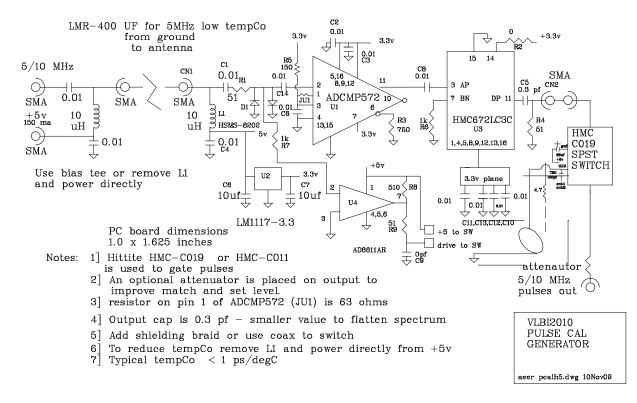

#### 1] Circuit

Figure 1 shows the circuit of the phase calibrator. The ADCMP572 ultrafast comparator provides sufficient gain to help ensure low sensitivity to the 5/10 MHz level. The HMC672LC3C ultrafast logic output is a square wave with very fast transitions (See MK5 memo #71). The output capacitor differentiates the waveform to generate positive and negative pulses. Pulses of one sign are passed by the HMC019 switch.

Figure 1. Circuit updated 9 November 2009

## 2] Output spectrum

The output spectrum is a series of "rails" or "tones" with 5 or 10 MHz spacing depending on the input frequency. The following table shows the rail strength and level of the undesired switch control waveform "feed thru" vs frequency. The feed through is given relative to the rail strength.

|             | 5 MHz         |          | 10 MHz |           |

|-------------|---------------|----------|--------|-----------|

| Freq. (GHz) | Rail strength | Feedthru | Rail   | Feed thru |

|             | (dBm)         | (dBc)    | (dBm)  | (dBc)     |

| 1           | -60           | -15      | -54    | -20       |

| 1.5         | -60           | -25      | -55    | -30       |

| 2.0         | -60           | -35      | -53    | -40       |

| 3.0         | -65           | <-40     | -56    | <-40      |

| 5.0         | -74           | <-40     | -64    | <-40      |

| 8.0         | -78           | <-40     | -69    | <-40      |

| 10.0        | -81           | <-40     | -74    | <-40      |

| 15.0        | -86           | <-40     | -80    | <-40      |

For comparison the output of the current tunnel diode pcal running at a 5 MHz pulse rate is about -80 dBm per rail at 8 GHz.

## 3] Temperature coefficient

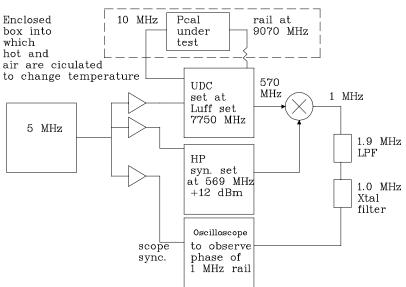

Figure 2 shows the set-up for measuring the temperature coefficient. The temperature of the pcal was cycled from 23 to 45 deg C. The following results were obtained from measurements of the phase rail at 9.07 GHz. For measurements at a 5 MHz rate the pcal was driven from a 5 MHz buffer instead of the 10 MHz output of the UDC.

Set-up to measure temperature coefficient of the pcal

Figure 2.

| Pulse rate MHz | Temp Co ps/degC |        |

|----------------|-----------------|--------|

| 5              | $0.0 \pm 0.5$   | Note 2 |

| 10*            | $+2 \pm 0.3$    | Note 1 |

Note 1 Measured in Feb. 09 before eliminating the power injection via bias tee.

Note 2 TempCo reduced from  $5\pm1$  ps/s after using +5v directly to the regulator and removing L1.

## 4] Comments

a. Output slope

The output slope can be controlled by the value of the HMC672 output capacitor C5. For radiated injection of the pcal the 1 pf might be a good choice. For injection via a broadband coupler C5 has been changed to 0.3 pf to reduce the signal level at the low frequency end.

b. Temperature coefficient

The temperature coefficient at 5 MHz is limited by the input offset drifts in the ADCMP572. The input voltage tempCo is  $10\mu V/\deg C$  which is equivalent to about 0.3 ps/degC at 5 MHz for a 1 volt signal. The resistor value on JU1 was originally 0 ohms 0402 resistor of 63 ohms may improve performance and this new value is recommended. If the bias tee method of power injection is to be used L1 should be a low tempCo inductor. The current part (Panasonic ELJ-PB100KF) has a ferrite cone with large temperature coefficient.

c. Output reflections.

Originally I thought that the differentiating capacitor should be after the microwave switch to reduce the relative level of the feed through the switch control waveform but since the differentiator provides a poor match it was found to be better to have the mismatch at only one place.

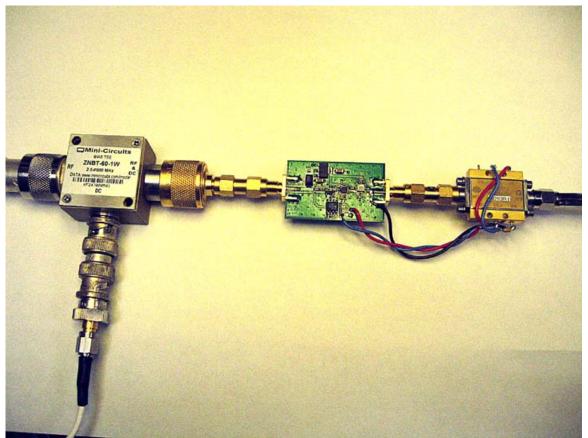

Figure 3. Pcal shown with bias tee power injection. Later versions use direct power injection for reduced temperature coefficient.

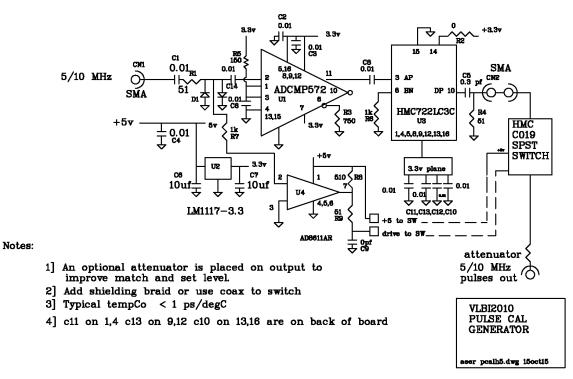

Figure 4. Updated circuit for PC board of Feb 2014.