VNDA:VLBA New Digital Architecture Walter Brisken & Lucas Hunt

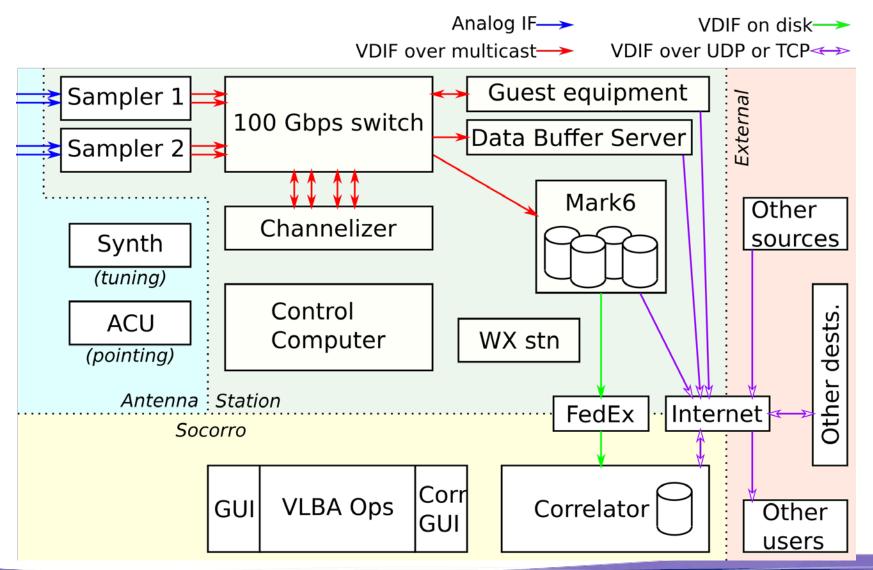

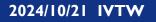

## VLBA New Digital Architecture

- Replace aging RDBEs with new, extensible architecture

- RDBEs are becoming difficult to maintain

- They have some design deficiencies that impact science and operations

- Driving VNDA requirements:

- Sample at > 8 bits per sample

- Avoid sampler resets to improve delay stability

- No user-visible tuning restrictions within bands

- One personality supporting all PFB & DDC modes

- To be fully backward compatible with RDBEs

- Use of commercially available equipment to degree possible

- Use standard interfaces wherever possible

- Extensible: support user-provided guest equipment

- E.g., spectrometer, pulsar backend, transient detector, ...

#### VLBA New Digital Architecture (VNDA)

# Initial approach (2018-2022)

- A first, ambitious, attempt ran into multiple problems

- Producer: Samplers connected via FMC to Vadatech FPGA PCIe board inside server

- Consumer: Vadatech FPGA board inside server

- Lessons learned

- Don't try to reinvent a full UDP stack in FPGA

- Data movement across PCIe at near maximum rate is challenging

- An isolated development group is less effective at solving major problems

## VNDA project reboot, 2023

- Look to use external experts

- Lean on successful projects using similar hardware

#### Producer

- Accepts 4 analog IF inputs

- Produce 4 digital IF outputs

- Sends to switch using multicast UDP

- Idea is that producer will run continuously without interruption. The configuration will be unchanged

- Ability to reset timing as necessary, should maintenance efforts disturb the 5 MHz clock

- Developed by Digital Radiometer Systems

## Producer Digitization and data broadcasting

- 2048 Msps output rate

- 14 bits per sample; packed into 16 bit words

- VDIF formatted data output, following VDIF Spec

- Each IF in its own VDIF stream

- No signal processing, only sample, time-tag, format, and broadcast

- Keep sample clock as stable as possible over long time periods

- Data broadcast using multicast UDP

## Timing and Monitor & control

- Reference Signal at 5 MHz

- Creates internal clock and IPPS from this

- I PPS signal to set absolute timing of the system

- Monitor points

- IPPS difference (difference between Internal IPPS and provided IPPS signal

- Loss of timing signal

- Other monitor points that follow from development

- Control

- Ability to trigger timing reset

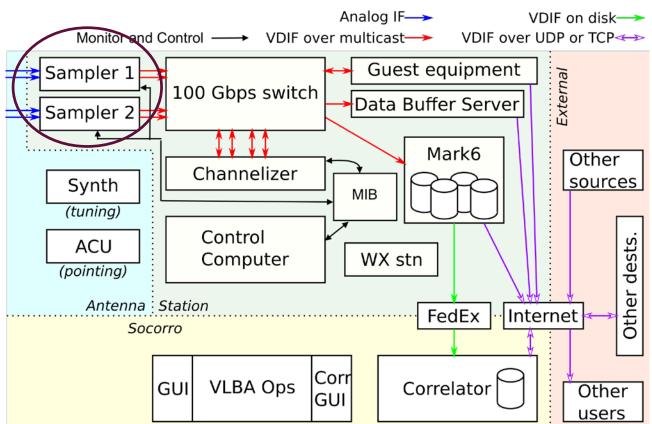

#### Hardware

- RFSoC 4x2 Manufactured by Real Digital, Recommended by Digital Radiometer Systems

- Entered production May, 2022

- Developed with input from Xilinx, and end users like CASPER

- Board is open source, board schematics, bill of materials, PCB Gerber files all available

- More information on specs available online

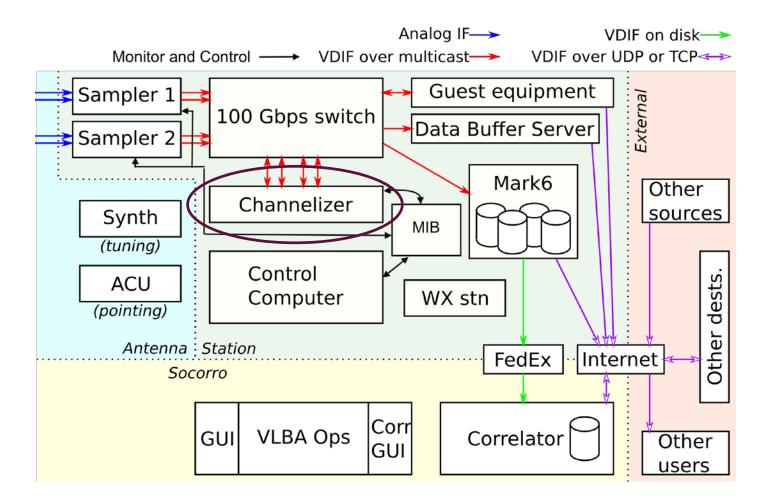

## Channelizer (or Consumer)

- Accepts 4 digital IF inputs

- Multicast UDP+VDIF packets from Producer through 100Gbps switch

- Digital signal processing, configured based on observing project setup

- Sends processed data back into switch using multicast UDP

- Development done by Fourier Space

# **Digital Signal Processing**

- Output selectable from any of the IF inputs

- Upper or lower sideband

- Bit depth selectable from 1, 2, 4 or 8 bits per sample.

- Choose bit depth for each channel

- Up to 32 output channels across all IFs, bandwidths from 1 to 1024 MHz

- Up to 16 output channels from any one IF

- Limited to 32 Gbps output

- Each channel tunable to arbitrary setpoint that is a multiple of 10 kHz from the input IF edge

## Monitor and Control

- Configure commands allow change of all or individual configuration parameters

- Validation command checks if configuration parameter set is valid

- Parameters can remain through entire observation or change from scan to scan.

- Monitor data available for

- Data acquisition performance

- Input and output ring buffer capacity/utilization

- Statistics of input and output time-series for each IF stream

- Information on DSP performance, power integration measurements

- Switched power measurements

#### Hardware

- One rack-mount server hosting 2+ GPUs

- Currently using supermicro server

- Hosts 2 high speed NICs for data receive and send

- Current hardware hosts 4 NVIDIA RTX A4000 GPUs

- COTS hardware is flexible, and this will likely change for deployment

- Hardware updates will be easier as GPUs become more powerful

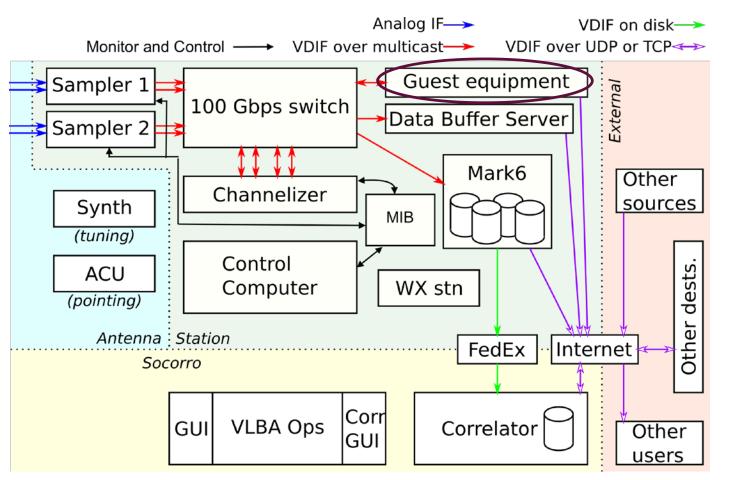

# Guest Equipment

- Multicast data passed through switch to guest equipment

- Guest equipment can subscribe to Sampler data or Channelizer data

- Ability to process data in real time and send relevant information over the internet

- Requirements

- Equipment to pass RFI testing

- NRAO need to safely shut down equipment for maintenance

- Subject to proposal and PM process

## Guest Equipment

- Commensal Observations

- A lot of guest equipment will likely be commensal instruments

- They will observe while other projects are observing

- NRAO will maintain the ability to turn off data flow to any desired guest equipment

- Current unknowns

- Rack space, power, and cooling are currently limited, resources for guest equipment hardware is currently unknown (or likely unavailable)

- Options for GE location: On site, Centralized rack at DSOC, Guest equipment owners site

- Tradeoffs for availability of data streams, Rackspace and power consumption issues

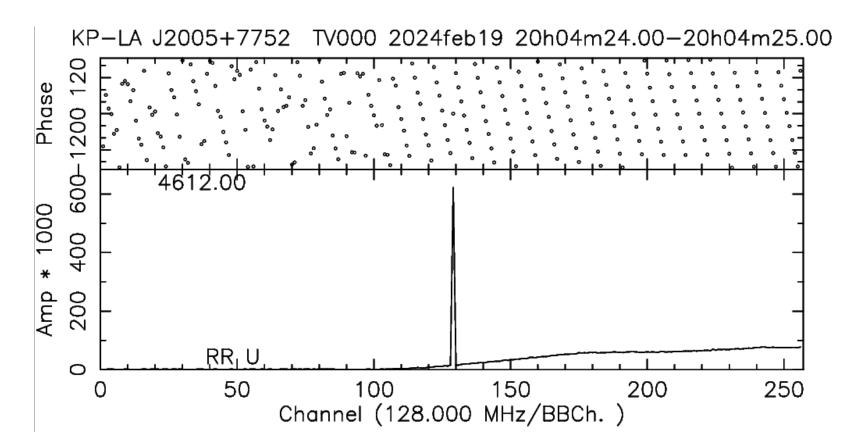

## Lab Testing Results

- Zero Baseline Test

- Send signal to RDBE and VNDA

- Correlate Signal

- See fringes!

- Everything worked as expected, moving to On The Sky testing

## Key VNDA Dates

- Phase 2

- Pass Preliminary Design Review

- Phase 3

- On the Sky testing

- Final design review

- Phase 4

- Instrument Commissioning

- On track to meet these dates currently

| Milestone                             | Rough<br>Date |

|---------------------------------------|---------------|

| Preliminary Design<br>Review Complete | 08/24         |

| On the Sky testing<br>complete        | 12/24         |

| Final design Review                   | 08/25         |

| Commissioning                         | 12/25         |

| Project closeout                      | 3/26          |

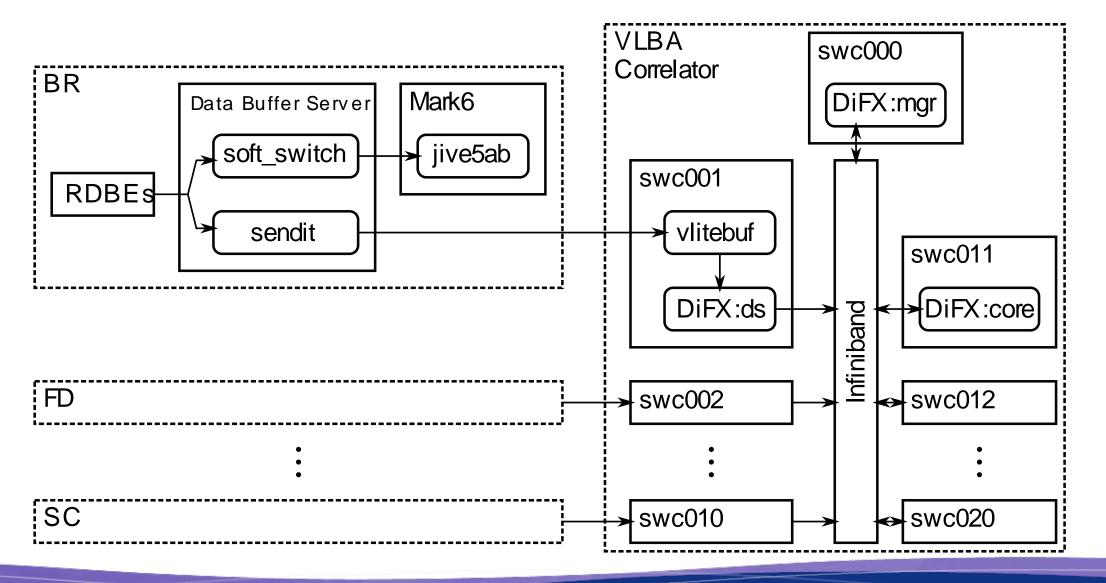

#### VNDA adjacent developments

- Real-time data transmission

- Goal: real-time correlation at 8 Gbps

- Intermediate steps:

- Real-time correlation at lower rates (currently 128 Mbps)

- Remote record of I+VLBA sites in Socorro

- Research-grade GNSS receivers

- In collaboration with ARL:UT

- Multi-band receive of all GNSS satellites

- Combined data to provide much improved "GPS minus maser" results

- Separate lines of site to provide direction-dependent calibration

- Direct correlation between GNSS and VLBI for frame tie (c.f., J. Skeens & J. York)

#### Real-time correlation with the VLBA

#### GNSS antenna at VLBA OV

Contact: lhunt@nrao.edu

#### www.nrao.edu science.nrao.edu

The National Radio Astronomy Observatory is a facility of the National Science Foundation operated under cooperative agreement by Associated Universities, Inc.

#### Server Rack Space and Power Usage

- G-Rack has 30U of space available, PDU has~1900W available (20A, 120V)

- Includes VNDA and VBER modules

- VNDA

- Producer 2U, 130W

- Consumer 4U, 700W

- Switches 2U, 270W

- Timing and Reference Distribution

- IPPS and 5 MHz signals each take up 1.5U, allocate 4U, 120W

- Data Buffer Server

- Allocated 2U space, 200W

- Estimated available space and power 16U, 500W

- Option for 1900W new circuit, not on building UPS

- Some retrofit costs to be expected if this is to be exercised