| 001 | Concept for an Affordable High-Data-Rate VLBI Recording and Playback System | A. Whitney | 19990930 |

| 002 | Interim report on COTS-VLBI Phase I Study | A. Whitney | 20010124 |

| 003 | Second interim report on COTS-VLBI project | A. Whitney | 20010308 |

| 004 | The Sustained Disc Streaming Performance of COTS Linux PCs | A. Mujunen | 20010713 |

| 005 | Preliminary design specifications for Mark 5 VLBI data system | A. Whitney | 20011115 |

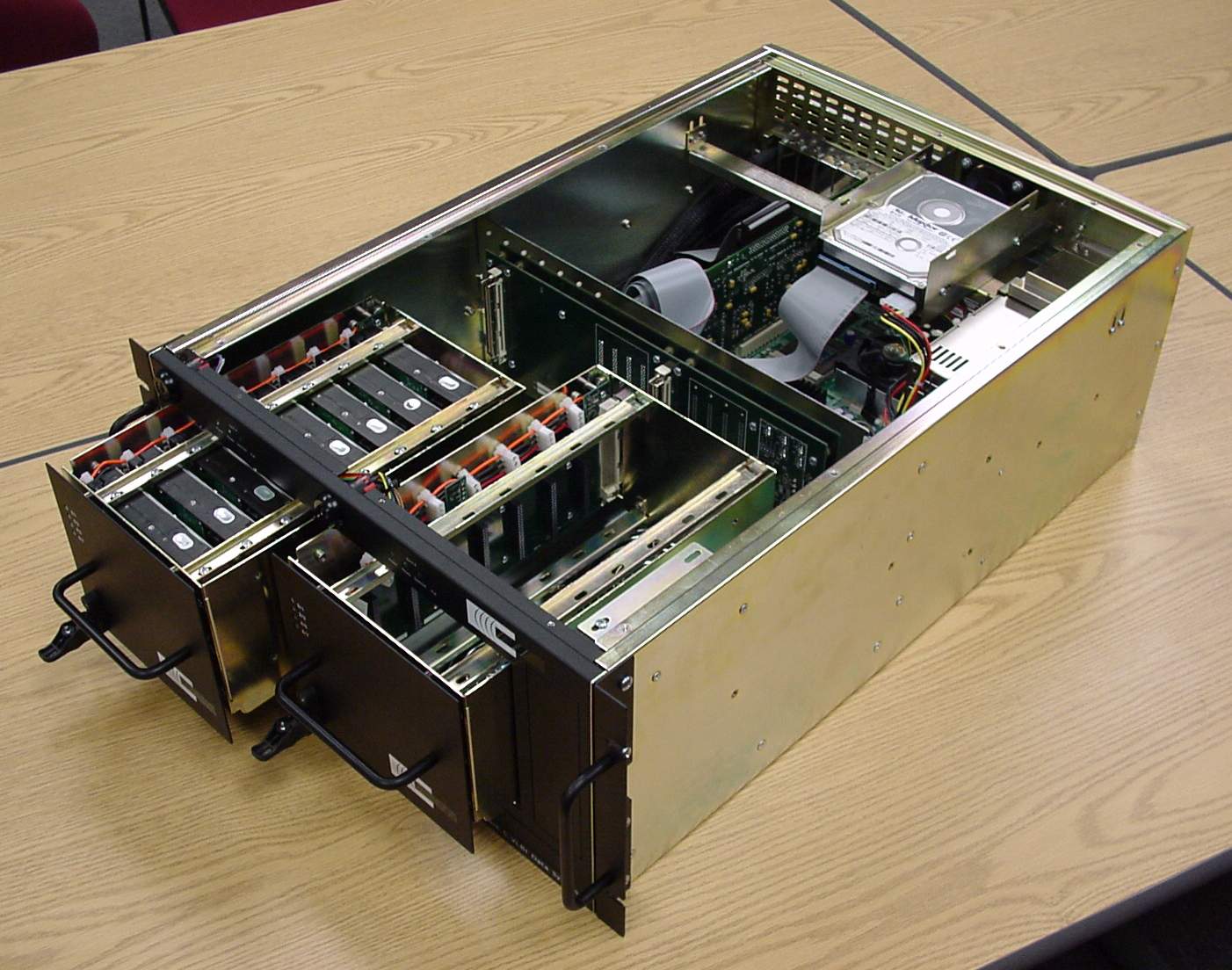

| 006 | Using a Mark 5 Prototype at Kokee | D.L. Smythe | 20011002 |

| 007.1 | The Mark 5A I/O Panel | D.L. Smythe | 20021224 |

| 008 | Mark 5A command set | A. Whitney, J.A. Ball | 20050204 |

| 009 | Mark 5A Input/Output Board Control/Status | A. Whitney | 20011010 |

| 010.1 | Mark 5 Adapter Modules | D.L. Smythe | 20020125 |

| 011.1 | Mark 5A Track Mapping | D.L. Smythe | 20011220 |

| 012.1 | Revised Mark 5 disc-management procedures | A.R. Whitney | 20020314 |

| 013 | Mark 5A Operating Modes | W. Aldrich | 20020104 |

| 014 | Recently Discovered Model Problems in the Mark 4 Correlator | R. Cappallo | 20030311 |

| 015 | Optimally Setting the kdiv Parameter in the Mark 4 Correlator | R. Cappallo | 20030311 |

| 016 | VSI Interface Board for the Mark 4 Formatter | D. Smythe | 20040107 |

| 017.1 | Programming the Mark 5A Input-Output Board | D. Smythe | 20040625 |

| 018 | Real to real polyphase filter bank | A. Rogers, H.F.H. | 20041119 |

| 019 | Mark 5B design specifications | A. Whitney, R. Cappallo | 20041124 |

| 020 | Simulation of phase cal and low fringe rate phase error using a polyphase filter bank | A. Rogers | 20041129 |

| 021 | Phase Cal Extraction for the Mark 5B | R. Cappallo | 20041130 |

| 022 | Mk4 Correlator System Timing | R. Cappallo | 20050103 |

| 023.1 | Mark 5B status LED’s – functions and layout | R. Cappallo | 20060414 |

| 024.4 | Mark 5B DIM parameters and procedures | A. Whitney, W. Aldrich | 20060427 |

| 025 | Mark 5B Prototype Test Plan | W. Aldrich | 20050208 |

| 026 | Mark5B DOM Software Register MAP Rev 1.6 | B. Fanous | 20051017 |

| 027 | Mark 5B DIM Checking | W. Aldrich | 20050608 |

| 028 | Windowing and PFB spectral efficiency | A. Rogers | 20051017 |

| 029 | DBE performance vs number of FIR and interpolator taps | A. Rogers | 20060117 |

| 030 | Delay Calculations for the Mk5B DOM | R. Cappallo | 20060131 |

| 031 | MARK 5B I/O BOARD Physical Description | W. Aldrich | 20051207 |

| 032 | Data Input Module Mark 5B I/O Board Theory of Operation | W. Aldrich | 20060117 |

| 033 | Zerobaseline test of DBE (Revised) | A. Rogers | 20060817 |

| 034.1 | Mark 5A Output FPGA Parameters | W. Aldrich | 20060512 |

| 035 | Mark 5B Data Output Module (DOM) Hardware Design Document | B. Fanous | 20060425 |

| 036 | Mark 5A+ design notes – Revision 3 | A. Whitney | 20060427 |

| 037 | Suggested algorithms for Mark 5A+ | A. Whitney | 20060427 |

| 038.2 | Hard Disks at High Altitude | D.L. Smythe | 20091120 |

| 039 | Mark 5A+ playback modes with Mark 5B recordings | A.R. Whitney | 20060621 |

| 040 | Mark 5B Board Schematics | A.R. Whitney | 20060712 |

| 041 | Mark 5B Board Component Layout | A.R. Whitney | 20051207 |

| 042 | 1024/2048 MHz clock synthesizer for DBE | A.E.E. Rogers | 20060817 |

| 043 | Simulations of broadband delay measurements | A.E.E. Rogers | 20060905 |

| 044 | Some thoughts on the calibration of broadband geodetic VLBI | A.E.E. Rogers | 20060905 |

| 045 | 5-meter VSI cable at 2048 Mb/s | D.L. Smythe | 20060911 |

| 046 | Specifications for enhanced Mark 5 module directory | A.R.Whitney et. al. | 20060818 |

| 047 | Timing Offset of the Mark 4 Formatter | D.L. Smythe | 20061010 |

| 048 | Cross-talk in dual channel DBE | A.E.E. Rogers, B. Fanous | 20061120 |

| 049 | Updated: Downloading Mark 5B Xilinx code | D.L. Smythe | 20100824 |

| 050 | Jumper settings for CIB and Serial Links | D.L. Smythe | 20061214 |

| 051 | Measurements of cross-talk and spurious signals levels | A.E.E. Rogers | 20070227 |

| 052 | Bench Testing the CIB | D.L. Smythe | 20070205 |

| 053 | Changing DMA Mode | D.L. Smythe | 20070216 |

| 054 | DOM Station Unit Operation | B.Fanous | 20070425 |

| 055 | DOM VSI Operation | B. Fanous | 20070425 |

| 056 | Preliminary performance characteristics of Up down converter | A.E.E. Rogers | 20071018 |

| 057 | Mark 5C Specification | Haystack/NRAO | 20080219 |

| 058 | Mark 5C Data-Frame Specification | Haystack/NRAO | 20080219 |

| 059 | Performance characteristics of Updown converter | A.E.E. Rogers | 20081103 |

| 060 | Temperature sensitivity of Updown converter | A.E.E. Rogers | 20071119 |

| 061 | Mark5C Sotware Interface Specification | Haystack/NRAO | 20080107 |

| 062 | Mark5C-, A Proposed Mark5C Emulator | Haystack/NRAO | 20080109 |

| 063.4 | Testing the Mark 5B (VSI4) Sampler Module | D.L. Smythe | 20100819 |

| 064.2 | Mark 5B(C) DIM Stand-alone testing | D.L. Smythe | 20130422 |

| 065 | Proposed phase calibration scheme | A.E.E. Rogers | 20080115 |

| 066 | Measurements of cable delay with temperature and flexure | A.E.E. Rogers | 20080213 |

| 067 | Dispersion and temperature effects in coax cables | A.E.E. Rogers | 20080226 |

| 068 | Measurements of Times Microwave Phase Track II 240 | A.E.E. Rogers | 20080226 |

| 069 | Temperature coefficients for LMR-400, LMR-400 ultraflex and LMR-240 (revised) | A.E.E. Rogers | 20091119 |

| 070 | Updown converter notes | A.E.E. Rogers | 20100225 |

| 071 | Test of Hittite Logic gate | A.E.E. Rogers | 20080417 |

| 072 | Simulations of NLTL pulse enhancement | A.E.E. Rogers | 20080422 |

| 073.2 | Mark 5B File Utility Programs | D.L. Smythe | 20090427 |

| 074 | Phase calibrator pulse distortion in UDC | A.E.E. Rogers | 20080618 |

| 075 | Preliminary circuit for the new phase cal. | A.E.E. Rogers | 20080714 |

| 076 | Mark5C Hardware Test and Acceptance Plan | C. Ruszczyk | 20081022 |

| 077 | Mark 5 Disk Drive Performance and Reliability | D.L. Smythe | 20090223 |

| 078 | Updated: Voltage and Temperature Monitoring on Intel S5000 Boards | D.L. Smythe | 20110215 |

| 079 | Updated DBE specifications | B. Fanous, A.R. Whitney | 20050906 |

| 080 | Solid State Drives with Mark 5 | D.L. Smythe | 20091207 |

| 081 | Specification for enhanced Mark 5 module directory Note: supersedes memo 046 | A.R. Whitney et al. | 20091210 |

| 082 | Remote Mark 5 Chassis Power Control | D.L. Smythe | 20110216 |

| 083 | Pressurized Disk Drives | D.L. Smythe | 20091229 |

| 084 | Revised: Cloning system disks | D.L. Smythe | 20100811 |

| 085 | Network Configuration for a Mark 5 | D.L. Smythe | 20100127 |

| 086 | Software correlator for station checks | A.E.E. Rogers | 20100205 |

| 087 | How to replace a CPU fan (and how not to) | D.L. Smythe | 20100216 |

| 088 | Mark 5 Disk Pack Temperature | M. Leeuwinga, H. Tenkink | 20100324 |

| 089.2 | StreamStor Utility Programs | D.L. Smythe, C.A. Ruszczyk | 20140409 |

| 090.1 | Digital Backend Software Command Set – Ver. 1.2 | C.A. Ruszczyk, M. Taveniku | 20120605 |

| 091.1 | Mark 5C Command Set Version 2.0 | A.R. Whitney et al. | 20120525 |

| 092 | Voltage and Temperature Sensors for Mark 5 Units | D.L. Smythe | 20111130 |

| 093 | Testing of RDBE PFBG version 1.4.1 | S.R. McWhirter | 20120120 |

| 094.1 | Conditioning Mark 5 Disk Modules | D.L. Smythe | 20130228 |

| 095 | How to determine the version of SDK installed on your Mark5 | C.A. Ruszczyk | 20140307 |

| 096 | Conduant V100 Controller Card SDK 9.2 Upgrade (Mark5A/B) with Debian Etch | C.A. Ruszczyk | 20140307 |

| 097 | Conduant XF2 Controller Card SDK 9.2 Upgrade (Mark5A/B) with Debian Etch | C.A. Ruszczyk | 20140307 |

| 098 | Conduant Amazon Controller Card SDK 9.2 Upgrade (Mark5B+) with Debian Etch | C.A. Ruszczyk | 20140307 |

| 099 | Conduant Amazon Controller Card SDK 9.3a Upgrade (Mark5B+) | C.A. Ruszczyk | 20140307 |

| 100 | Mark5 User Directory Formats | C.A. Ruszczyk, B. Eldering, H. Verkouter | 20140327 |

| 101 | Notes on KOKEE20M phase cal | B. Corey | 20181106 |